4H-SiC (Silicon Carbide) is an important wide bandgap semiconductor material widely used in high-temperature, high-frequency, and high-power electronic devices. To enhance the performance of 4H-SiC devices, it is crucial to minimize defects during the epitaxial growth process. Below are some methods for controlling defects in 4H-SiC homoepitaxial growth:

1. Substrate Treatment

Surface Cleaning: Before epitaxial growth, chemical cleaning and high-temperature annealing are used to remove contaminants and oxide layers from the SiC substrate surface.

Surface Planarization: Chemical mechanical polishing (CMP) or thermal treatment is employed to make the substrate surface smoother, reducing the impact of microparticles and surface defects on the epitaxial layer.

2. Optimization of Epitaxial Growth Process

Growth Temperature Control: Optimizing the growth temperature is crucial for reducing defects. Generally, higher growth temperatures help reduce screw dislocations and step defects.

Adjustment of Carbon/Silicon Ratio (C/Si): Adjusting the C/Si ratio in the reactive gases during vapor phase deposition can effectively reduce stacking faults and three-screw dislocations.

Growth Rate Control: Lower growth rates help reduce defect density, but a balance between production efficiency and defect control needs to be achieved.

3. Use of Buffer Layers

Buffer Layer Design: Growing a buffer layer between the substrate and the epitaxial layer can alleviate stress caused by differences in thermal expansion coefficients and lattice mismatch, thus reducing defect density.

Graded Buffer Layers: Gradually changing the composition of the buffer layer ensures a smoother transition between the epitaxial layer and the substrate, thereby reducing interface defects.

4. Post-treatment of Epitaxial Layers

High-Temperature Annealing: Post-growth high-temperature annealing can repair some of the defects generated during the growth process.

Doping Control: Appropriate doping (e.g., aluminum, nitrogen) can influence defect formation and diffusion, thereby controlling defect density.

5. Surface Monitoring and Feedback

In-situ Monitoring: Using in-situ monitoring techniques (such as Reflection High-Energy Electron Diffraction, RHEED) to monitor the surface state and growth mode during the epitaxial growth process in real-time.

Surface Analysis: Employing tools like AFM (Atomic Force Microscopy) and SEM (Scanning Electron Microscopy) to analyze the surface of the grown epitaxial layer, providing timely adjustments to the growth parameters.

6. Advanced Growth Techniques

Chemical Vapor Deposition (CVD): Optimizing CVD process parameters (such as pressure, gas flow rate, and gas composition) to reduce defects.

Molecular Beam Epitaxy (MBE): Although MBE is costlier, it allows atomic-level control, which helps in reducing defects.

By implementing the aforementioned methods, defects in 4H-SiC homoepitaxial growth can be effectively controlled, thereby improving the quality of the material and the performance of the devices. Specific optimization methods need to be adjusted and validated based on actual equipment and process conditions.

Related product links

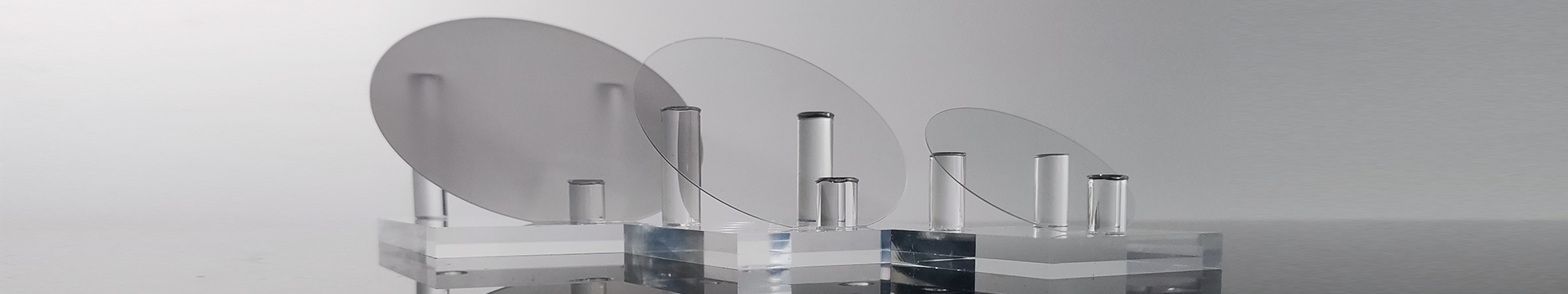

Silicon Carbide Wafer (SiC Wafer)

As third-generation semiconductor materials such as silicon carbide (SiC) and gallium nitride (GaN) continue t...

With the continuous advancement of power electronics, RF devices, and optoelectronic technologies, the demand ...

The selection of substrate materials plays a crucial role in the development of high-frequency, high-power RF ...