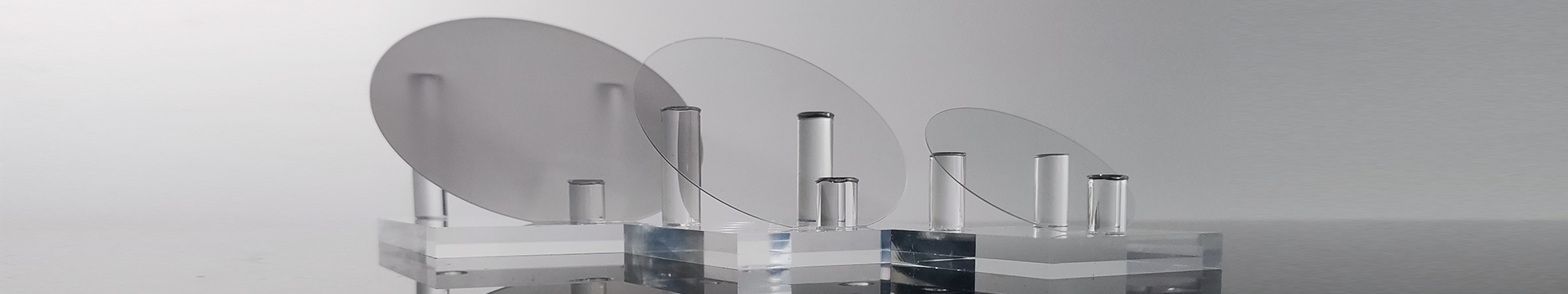

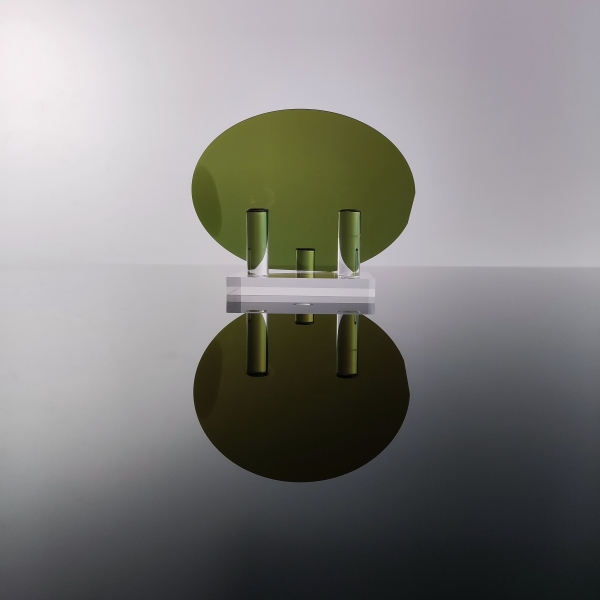

In silicon carbide (SiC) wafer manufacturing, orientation flats (flat edges) and notches are two common methods used to indicate the wafer’s crystal orientation and axes, aiding precise alignment during the manufacturing and handling processes. The choice between these two marking designs reflects different technical and process requirements, and is influenced by factors such as wafer size, equipment compatibility, and cost control. For those interested in 6-inch SiC wafers, you can find more information or purchase them through this product link.

This article explores why 6-inch (150mm) wafers still predominantly use orientation flats rather than notches and analyzes the advantages and disadvantages of both marking methods.

1. Why Do 6-Inch Wafers Still Use Orientation Flats?

1.1 Equipment Compatibility

6-inch wafers are widely used in mature markets such as power semiconductors, where manufacturing equipment tends to rely on more traditional designs, often using orientation flats for crystal alignment. These pieces of equipment were originally designed to reference the flat edge for alignment, providing a sufficient basis for determining crystal orientation. Switching to a notch would require retrofitting or replacing this equipment, resulting in significant cost increases.

1.2 Cost Considerations

Continuing to use orientation flats on 6-inch wafers helps to keep production costs down. The flat-edge technology is well-established, and many manufacturers can continue producing 6-inch wafers without making additional investments in equipment or processes. This is particularly important for cost-sensitive industries like power semiconductors.

1.3 Market Demand

6-inch wafers are commonly found in applications such as power electronics and sensors, markets that generally have less stringent demands for automated alignment precision. Unlike logic chips or memory devices, where fine tolerances are essential, silicon carbide power devices have more relaxed alignment requirements. Therefore, orientation flats are sufficient to meet the manufacturing needs in these sectors.

2. Technical Comparison Between Orientation Flats and Notches

2.1 Orientation Flats

Advantages:

High equipment compatibility: Many legacy wafer processing systems are designed around orientation flats, making them widely applicable in the production of 6-inch and smaller wafers.

Lower costs: The processes related to flat edges are highly mature, with equipment and workflows that are well-established, resulting in lower operational and maintenance costs. There’s no need to introduce complex automation systems for these wafers, helping to minimize production expenses.

Mature technology: As one of the earliest methods adopted in the semiconductor industry, orientation flats have a long-standing presence and offer a simple, reliable manufacturing process.

Disadvantages:

Lower alignment precision: Compared to notches, orientation flats offer less precision in crystal alignment, especially in highly automated processes, where alignment errors may impact subsequent manufacturing steps.

Material waste: The flat edge design requires removing a portion of the wafer, leading to material waste, particularly in smaller wafers where the loss is proportionally more significant.

2.2 Notches

Advantages:

Higher alignment precision: Notches provide a more modern solution for wafer marking, enabling higher precision alignment in automated equipment. Their accuracy in indicating crystal orientation makes them ideal for processes that demand tight tolerances.

Maximized material usage: Since notches involve removing less material than flat edges, they allow for better material utilization, maximizing the available wafer surface area.

Ideal for high-automation environments: Notches integrate seamlessly with modern automated manufacturing systems, making them the preferred option for 200mm and larger wafers, especially in high-precision fabrication environments.

Disadvantages:

Higher equipment and process costs: Notches require specialized equipment and alignment systems. For existing production lines, adopting notches might necessitate substantial capital investments to upgrade or replace equipment.

More complex maintenance: The automation systems associated with notch-based alignment are more intricate, leading to increased maintenance costs and technical support requirements, which raises the overall cost of operation.

3. Application Scenarios for Orientation Flats and Notches

Orientation flats are primarily used in the production of 6-inch and smaller wafers, particularly in industries with less stringent automation needs, such as power devices and other mature markets. The flat edge design meets these sectors’ demands while maintaining equipment compatibility and keeping production costs low.

Notches, on the other hand, are more commonly found in larger wafers (200mm and 300mm), especially in modern logic chip and memory device manufacturing. Their high precision and material efficiency make notches indispensable in processes that require tight tolerances and high levels of automation.

Conclusion

The use of orientation flats and notches on silicon carbide wafers represents different technical choices in semiconductor manufacturing. Orientation flats are widely employed in the production of 6-inch and smaller wafers due to their lower cost and high equipment compatibility, making them well-suited for the power semiconductor and other mature markets. Notches, with their superior alignment precision and material efficiency, are preferred in the production of larger wafers, particularly where high-precision and automated processes are essential.

Manufacturers must weigh the factors of equipment upgrades, cost management, and process requirements when choosing between these two marking methods, aiming to optimize production efficiency and economic outcomes.

As semiconductor technology advances, Gallium Nitride (GaN) has become a core material in optoelectronics, rad...

With the rapid advancement of third-generation semiconductor technologies, Silicon Carbide (SiC) has emerged a...

As third-generation semiconductor materials such as silicon carbide (SiC) and gallium nitride (GaN) continue t...