Sapphire substrate fabrication follows a well-defined progression from coarse material shaping to precision finishing. The complete process flow is:

Crystal Growth → Orientation & Rounding → Multi-Wire Slicing → Grinding → CMP Polishing → Cleaning & Inspection

Each downstream process step is designed to remove the surface and subsurface damage introduced by the previous one, while continuously improving surface flatness, roughness, and structural integrity.

Multi-wire slicing utilizes a high-speed steel wire looped around multiple guide wheels, carrying SiC or diamond abrasive slurry. Material is removed primarily through brittle-mode fracture as free abrasives roll, press, and scratch the crystal, functioning like a wire saw to slice the sapphire ingot into wafers.

• Macroscopic: Pronounced, directionally uniform wire-saw marks.

• Microscopic: Abundant brittle pits, micro-cracks, and a heavily damaged fracture layer caused by chipping-dominated removal.

• Ra: 0.5–2.0 μm (500–2000 nm) — extremely rough.

• Characteristics: Large variations due to the coexistence of macro-scale saw marks and micro-scale crack networks.

Sliced wafers cannot be used directly for epitaxy or device fabrication. Their high roughness and deep subsurface damage drastically degrade epitaxial film quality and reduce device yield.

This stage focuses on geometric shaping and thickness preparation for subsequent precision processing.

Grinding employs fixed or semi-fixed diamond abrasives (grinding plates or slurry). Material removal transitions from brittle-mode to a mixed brittle-ductile mode, significantly reducing damage depth.

• Macroscopic: Wire-saw marks are removed; the surface becomes uniform and matte.

• Microscopic: Brittle pits and deep cracks are eliminated but replaced by uniform grinding scratches and shallow plastic deformation grooves.

• Ra: 0.1–0.5 μm (100–500 nm).

• Characteristics: Roughness decreases by an order of magnitude, though visible mechanical scratches remain.

Ground wafers also cannot meet the requirements of high-end epitaxy due to residual scratches and plastic deformation.

This step focuses on rapid thickness reduction, warp/bow correction, and removal of most slicing damage to prepare for CMP.

For lower-end applications—such as industrial windows or wear-resistant components—properly cleaned ground wafers may be used directly.

Chemical Mechanical Polishing (CMP) integrates surface chemical reaction and gentle mechanical abrasion:

• Chemical: The slurry (acidic or alkaline) reacts with the sapphire surface, generating a soft hydrated layer (e.g., AlOOH).

• Mechanical: A polishing pad and nanoscale abrasives (e.g., colloidal silica) remove this softened layer through uniform shear.

The cycle produces highly controlled ductile-mode removal with negligible new damage.

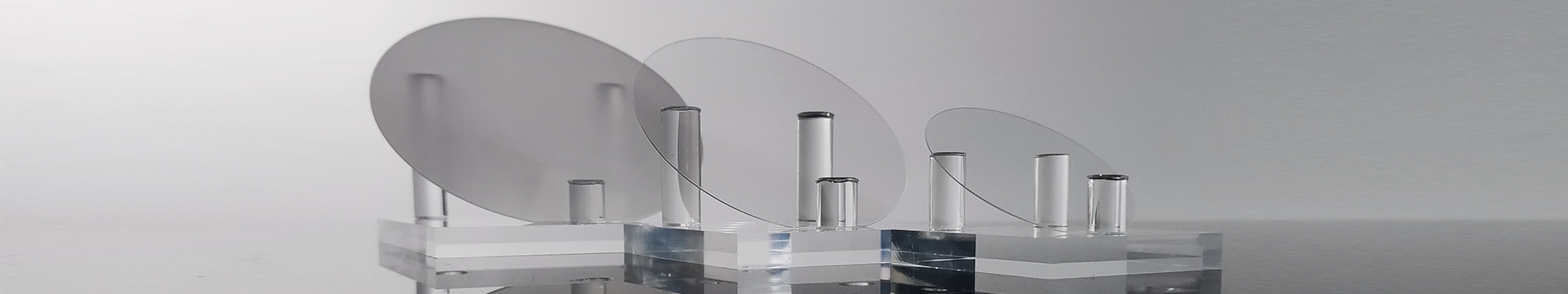

• Macroscopic: Mirror-like surface capable of clear image reflection.

• Microscopic: Atomic-level step-flow structure with no scratches, cracks, or deformation layer (confirmed by AFM).

• Ra: < 0.5 nm; high-end products can achieve < 0.2 nm.

• Characteristics: Roughness is reduced by approximately three orders of magnitude compared with ground wafers.

CMP-polished wafers represent the final device-grade state, suitable for all high-performance applications:

• LED epitaxy (largest market): Ensures high-quality GaN growth, directly impacting efficiency and lifetime.

• RF devices: Essential for low-loss GaN-on-Sapphire RF components (e.g., smartphone filters).

• Lasers: Required for low-scattering GaN laser diode structures.

• Optical windows: Aerospace and defense-grade optics demand superior transparency and scratch resistance.

• Consumer electronics: Camera lens covers, smartwatch sapphire glass, and other premium optical components.

Sapphire substrate fabrication is a progressive refinement sequence in which each step eliminates the mechanical and structural damage caused by the previous one. The workflow evolves from:

• Coarse geometric shaping,

• Precision planarization,

• Atomic-level smoothing,

ultimately producing substrates that satisfy stringent requirements for geometry, crystallinity, and surface perfection across advanced semiconductor and optical applications.

JXT Technology Co.,Ltd. supplies 2–12 inch sapphire substrates in a full range of crystallographic orientations:

• C-plane <0001>

• R-plane <1-102>

• M-plane <1-100>

• A-plane <11-20>

Available services include:

• Patterned Sapphire Substrates (PSS / NPSS)

• High-precision sapphire laser cutting

• Custom sapphire carriers (Sapphire Carrier)

IntroductionWith the rapid growth of electric vehicles, photovoltaic energy storage syst...

IntroductionAs the demand for high-efficiency power electronics continues to grow, silic...

With the rapid development of advanced manufacturing, aerospace systems, deep-earth ener...